## A Second-Order Single Loop Oversampling Analog-to-Digital Converter (ADC) with Proposed Hybrid Feedforward/Feedback Architecture

Hasan M. Azzawi Electrical Engineering Department, University of Technology/Baghdad Email: hasansas82@yahoo.com

#### Received on: 19/10/2011 & Accepted on: 5/4/2012

#### ABSTRACT

This paper proposes hybrid architecture of feedforward/feedback second order single-loop modulator for high resolution analog-to-digital converter (ADC) applications. Different techniques for oversampling modulator are discussed. The proposed architecture consists of three stages. The first stage is  $2^{nd}$  order single loop oversampling ADC with novel feedforward/feedback architecture. In the second stage, an error cancellation circuit (ECC) is proposed at the output of the modulator to noise shaping of quantization noise. In addition, the third stage is a decimation filter in order to reduce the oversampling ratio (OSR) which is suitable for broadband applications. With low OSR=24, the signal-to-noise ratio (SNR) is improved about 55 dB if compared with traditional architecture (feedback singleloop high order topology). The achieved resolution or the effective number of bits (ENOB) is (22-bit). With high OSR=256, the net improvement in quantization noise reduction is 64 dB if compared with feedforward architecture (single-loop high order) and the ENOB=28. Finally a 1-bit quantizer is used in the proposed architecture which greatly decreases the circuit implementation complexity and power consumption. Simulation results show the superiority performance of proposed hybrid architecture as compared with traditional modulator topologies (feedforward and feedback).

Keywords: ADC, feedforward, feedback, single-loop high order converter.

# محول ألاشاره الكمية الى الرقمية عالي العينة من الدرجة الثانية بمعمارية هجينة مقترحة (التغذية الامامية/التغذية العكسية)

السخسلاصية

يقترح هذا البحث معمارية هجينة لمضمن الاشارة من الدرجة الثانية لتطبيقات محول الاشارة الكمية الى الرقمية عالية الدقة. تم مناقشة عدة تقنيات لمضمن الاشارة عالي العينة. المعمارية المقترحة تتكون من ثلاث مراحل. المرحلة الاولى هي محول الاشارة الكمية الى الرقمية من الدرجة الثانية بمعمارية جديدة (Feedforward/Feedback). المرحلة الثانية هي دائرة الغاء

https://doi.org/10.30684/etj.30.13.5 2412-0758/University of Technology-Iraq, Baghdad, Iraq This is an open access article under the CC BY 4.0 license http://creativecommons.org/licenses/bv/4.0

الخطأ المقترحة لتقليل ضوضاء التكمية (Quantization noise) عند محول الاشارة المقترح. أضافة الى ذلك المرحلة الثالثة هي (Decimation filter) لتقليل معدل عالي العينة (OSR) وهو مناسب لتطبيقات الحزمة العريضة. عند OSR منخفض، تم تخفيض ضوضاء التكمية Peedback (55 dB) اذ ماتم مقارنتة مع معمارية التغذية العكسية التقليدية (Soge date the peedback ) من نوع(55 db) اذ ماتم مقارنته مع معمارية التغذية العكسية التقليدية (Ose date date (architecture) من نوع(6 db) اذ ماتم مقارنته مع معمارية التغذية العكسية التكمية بقدار (25 db) النظام المقترح عند Ose عالي، تم تخفيض ضوضاء التكمية بمقدار (22-bit) من نوع(22-bit) النظام المقترح عند Ose عالي، تم تخفيض ضوضاء التكمية بمقدار (6 db) اذ ماتم مقارنتة مع معمارية التغذية الامامية (22-bit) من نوع (I-bit) من نوع (Single-loop high order) من نوع (Quantizer) في المعمارية المقترحة والتي تخفض من تعقيد بناء الدائرة و من استهلاك الطاقة. اظهرت نتائج المحاكاة أداء متفوقا لمعمارية الهجينة المقترحة عند المقارنة مع معارية المقدرة والتي تخفض من تعقيد بناء الدائرة و من استهلاك الطاقة. اظهرت نتائج المحاكاة أداء متفوقا لمعمارية الهجينة المقترحة عند المقارنة مع معارية المقدرة والتي تخفض من تعقيد بناء الدائرة و من استهلاك الطاقة.

#### INTRODUCTION

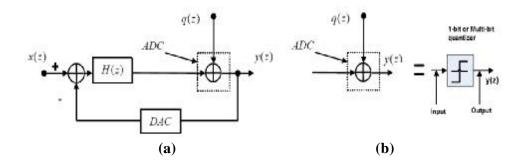

ith the recent developments in both wired and wireless communications, there is a need to analog-to-digital converters (ADCs) at megahertz (MHz) with high resolution at low voltage environments [1]. Conventional ADC architectures (Flash and successive approximation) are not suitable for high resolution applications because of the need to near-ideal analog components and/or precise trimming. To implement a high resolution ADC converter, the oversampling modulator is considered a suitable approach and widely used due to its simplicity and effectiveness [2]. Oversampling ADC or delta-sigma converter, as shown in fig.1 is based on the principle that the input signal is oversampled and the quantization noise is shaped and later removed by digital filters. The oversampling ratio (OSR) is defined as [3]:

$$OSR = \frac{f_s}{f_{Ny}} \tag{1}$$

Where:  $f_s$  = sampling frequency,

$f_{Nv}$  = Nyquist rate.

The in-band quantization noise power  $(N_q^2)$  with oversampling is given by [3]:

$$N_{q}^{2} = \frac{S_{q}^{2}}{f_{s}} \int_{-f_{b}}^{f_{b}} df = \frac{S_{q}^{2}}{OSR}$$

(2)

Where:  $f_b = \text{signal bandwidth}$ ,

$s_q^2$  = the noise power.

Compared to a Nyquist rate converter, the noise power is reduced by OSR. The noise shaping filter of converter distributes the quantization error or noise so as to be very low in the band of interest. By using superposition, the loop output of fig.(1a) is determined as:

$$y(z) = \frac{H(z)}{1 + H(z)} . x(z) + \frac{1}{1 + H(z)} . q(z)$$

(3)

Where: H (z) =  $Z^{-1}/(1 - Z^{-1})$ .

Two transfer functions are used to determine ADC performance, a Signal Transfer Function of the system (STF) and a Noise Transfer Function of the system (NTF). These transfer functions are given by [3]:

$$STF(z) = \frac{y(z)}{x(z)}\Big|_{q(z)=0} = \frac{H(z)}{1+H(z)} = Z^{-1}$$

(4)

$$NTF(z) = \frac{x(z)}{q(z)}\Big|_{x(z)=0} = \frac{1}{1+H(z)} = (1-Z^{-1})$$

(5)

Substituting equations (4) and (5) by equation (3), the loop output is determined as:

$$y(z) = x(z).Z^{-1} + q(z).(1 - Z^{-1})$$

(6)

Where: x(z) is input signal, STF (Signal Transfer Function) =  $z^{-1}$ , y(z) is output signal and q(z) is quantization noise of the converter, as shown in fig.(1b).

A general NTF (Noise Transfer Function) for high order converter is given by [3]:

$$N_{q}(z) = (1 - z^{-1})^{L} \times q(z)$$

(7)

Where: L is the converter order. The ideal SNR of converter is given by [4]:

$$SNR = 10.Log \frac{3}{2} \cdot \frac{(2L+1)}{p^{2L}} \cdot (OSR)^{2L+1}$$

(8)

Where: L is the converter order.

And the resolution bits or the effective number of bits (ENOB) is given by [3]:

$$ENOB = (SNR - 1.76)/6.02$$

(9)

Increasing the order of the converter improves the performance. In general, for an L-order modulator, the SNR improvement is (6L+3) dB or (L+0.5) bits per doubling the OSR [5].

## **OVERSAMPLING CONVERTER TOPOLOGIES**

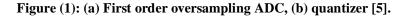

The single-loop high order oversampling converter topology can be divided into two classes: feedback (FB) and feedforward (FF) [3,7].

## **Feedback Topology**

The feedback architecture, as shown in fig.(2a), is the most commonly used topology of oversampling ADC. The output can be expressed as [6]:

$$y(z) = x(z)z^{-2} + q(z)(1 - z^{-1})^2$$

(10)

The NTF provides a second-order noise-shaping function for the quantization noise of the converter.

The output signals of the first and second integrators,  $(v_1(z) \text{ and } v_2(z))$ , are as follows:

$$v_1(z) = z^{-1}(1-z^{-1})x(z) - z^{-1}(1-z^{-1})q(z)$$

(11)

$$v_2(z) = z^{-2}x(z) - z^{-1}(2 - z^{-1})q(z)$$

(12)

From equations (11) and (12), the output signals of two integrators  $(v_1(z) \text{ and } v_2(z))$  are the functions of x(z), the input signal to the converter. Then the signal swing at the output of amplifiers becoming large which makes their implementation in the low-voltage more difficult. The harmonics generated by the amplifier non-linarites also depends on the signal swing of integrator, which severely reduces the SNDR (signal-to-noise and distortion) of the converter with feedback topology.

#### **Feedforward Topology**

The output of the feedforward converter as shown in fig.(2b) can be expressed as [6]:

$$y(z) = x(z) + v_1(z) + v_2(z) + q(z)$$

(13)

The output signals of the first and second integrators  $(v_1(z) \text{ and } v_2(z))$  are as follows:

$$v_1(z) = -z^{-1}(1-z^{-1})q(z)$$

(14)

$$v_2(z) = -z^{-2}q(z) \tag{15}$$

Equations (14) and (15) shows that the output signals of two integrators  $(v_1(z) \text{ and } v_2(z))$  are without the input signal x(z), which means that the feedforward converter processes quantization error only. Substituting equations (14) and (15) by equation (13), the loop output is determined as:

$$y(z) = x(z) + q(z)(1 - z^{-1})^2$$

(16)

$$STF = 1 \tag{17}$$

$$NTF(z) = (1 - Z^{-1})^2$$

(18)

Compared with feedback topology, the NTF given by equation (18) is the same as equation. (5), while the STF is unity under ideal circumstances and not delayed.

Therefore, the signal swings passing through the integrator are smaller and the distortion generated by the non-linearities effect of the amplifiers is input signal independent. It can be significantly reduced. Furthermore, in this topology, the signal amplitude of the amplifiers is reduced and that eases implementation of amplifier design. However, it is more suitable for low-power applications.

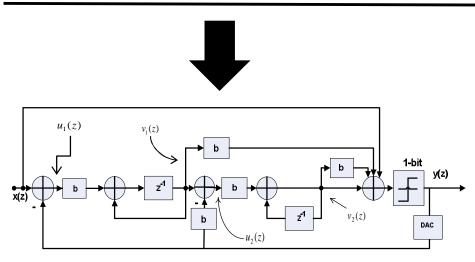

## PROPOSED HYBRID ARCHITECTURE OF FEED-FORWARD/ FEEDBACK ADC

#### **Proposed Converter Architecture**

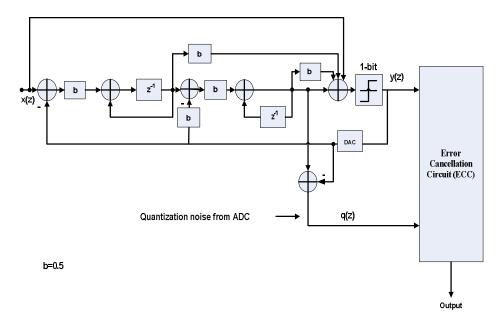

In this paper, a combination of feedforward topology and feedback topology is proposed. The general structure of the proposed (I) feedforword/feedback second order single loop converter is shown in fig.(2c). The input and output of the proposed feedforward/feedback oversampling ADC can be expressed as:

$$u_1(z) = x(z) - y(z)$$

(19)

$$v_1(z) = u_1(z).b + v_1(z).z^{-1}$$

(20)

|                                                                             | to-Digital Converter (ADC) with Proposed<br>Hybrid Feedforward/Feedback Architectu |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| $v_1(z)(1-z^{-1}) = u_1(z)(1-z^{-1})$                                       | (z).b (21)                                                                         |

| $v_1(z)(1-z^{-1}) = x(z)$                                                   | $z).b - y(z).b \tag{22}$                                                           |

| $v_{1}(z) = \frac{x(z)b - y(z)}{(1 - z^{-1})}$ $u_{2}(z) = v_{1}(z) - y(z)$ | (23)                                                                               |

| $v_2(z) = u_2(z) + v_2$                                                     | $(z).z^{-1}$ (25)                                                                  |

| $v_2(z)(1-z^{-1}) = u_2$                                                    | (z) (26)                                                                           |

| $v_2(z)(1-z^{-1}) = v_1$                                                    | (z) - y(z).b (27)                                                                  |

| $v_2(z) = \frac{v_1(z) - y(z)}{(1 - z^{-1})^2}$                             | (28)                                                                               |

$$\therefore v_2(z) = b \cdot \frac{x(z) - y(z) \cdot (2 - z^{-1})}{(1 - z^{-1})^2}$$

(29)

Combining the outputs of the modulators as shown in fig.(2c), the output of the entire stage is given by:

$$y(z) = v_1(z)b + v_2(1+b) + x(z) + q(z)$$

(30)

Substituting equations (23) and (29) in equation (30), and assume b=1, the final output is given by:

$$y(z) = x(z) \cdot \frac{(4 - 3z^{-1} + z^{-2})}{(6 - 5z^{-1} + z^{-2})} + e(z) \cdot \frac{(1 - z^{-1})^2}{(6 - 5z^{-1} + z^{-2})}$$

(31)

The SNR of the proposed architecture is [5]:

$$SNR = 10 \log_{10} \left(\frac{S_q^2}{S_e^2}\right) + 10 \log_{10} (OSR) dB$$

(32)

Where:  $s_{e}^{2} = \Delta^{2}/12$ ,  $\Delta$  =step size of quantizer.

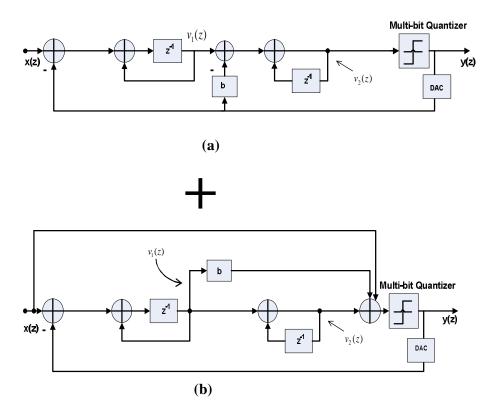

Fig.(3) shows the proposed architecture of feedforward/feedback oversampling ADC with proposed error cancelation circuit at the output. It is a 1-bit quantizer second-order structure with single-loop topology. The proposed novel (I) architecture has following features:

- 1. The feedforward and feedback signals are summed at the output of the first integrator, and then fed to the second integrator stage.

- 2. The summation point of feedforward paths before the quantizer in fig.(3a), is necessary to realize all the feedforward signals summed together, which creates feedforward/feedback oversampling ADC.

- 3. The gain coefficients (b) is chosen for maximizing peak SNDR best performance, and maintain loop stability of the converter. Another consideration in choosing the gain is to guarantee that the baseband quantization noise is independent of the input signal, thereby avoiding the presence of harmonics in the noise floor and decreasing the SNDR, since the harmonics are evident when  $b \ge 3$  [7].

- 4. The drawback of multi-bit quantizer is the need for high linearity in the feedback digital-to-analog converter (DAC). Unfortunately, much of the power savings of multi bit quantization are lost owing to the complexity of the techniques that must be used to linearize the output of this DAC. According to this, a second order single-loop topology with one-bit quantizer has been chosen in this paper, in order to reduce the complexity (no needed for data weighted averaging (DWA) technique in feedback path to reduce the linear error caused by the DAC as design in Ref.[8]) and power dissipation that has more benefits than the higher order and cascade modulators for implementation [9].

## **Error Cancellation Circuit (ECC)**

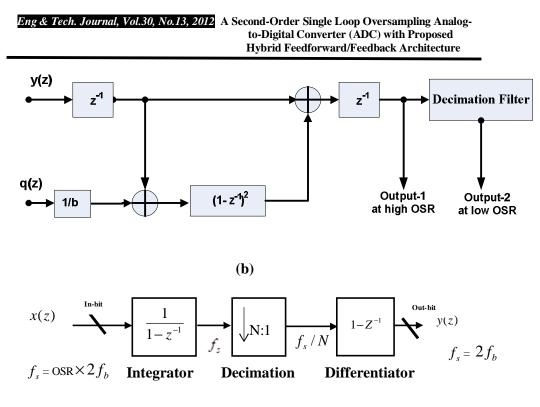

An error cancellation circuit is proposed for single loop high-order in order to eliminate any distortions introduced by the quantization stage. The digital cancellation circuit, as shown in fig.(3b), is required to combine multi input and to eliminate of in-band quantization noise and tone at output of converter. The in-band error quantization noise is shaping to out-of-band by using a second order NTF of ECC. The input and output of the proposed ECC can be expressed as:

$$Ou(z) = y(z) \cdot z^{-2} + (1 - z^{-1})^2 \cdot (y(z) \cdot z^{-1} + \frac{1}{h} \cdot q(z))$$

(33)

And the final output of ECC is:

$$Out(z) = y(z).(z^{-1} - z^{-2} + z^{-3}) + \frac{1}{b}.(1 - z^{-1})^2 q(z))$$

(34)

The NTF of proposed ECC is:

$$NTF = (1 - Z^{-1})^2 \tag{35}$$

#### **Decimation Filter**

The decimation filter has following features [10]:

- 1. Remove shaped quantization noise: The modulator is designed to suppress quantization noise in the baseband. Thus, most of the quantization noise is at frequencies above the baseband. The main objective of the digital filter is to remove this out-of-band quantization noise. This leaves a small amount of baseband quantization noise and the band-limited input signal component. Reducing the baseband quantization of the digital output.

- 2. Decimation (sample rate reduction): The output of the modulator is at a very high sampling rate. After the high frequency quantization noise is filtered out, it is possible to reduce the sampling rate. It is desirable to bring the sampling rate down to the Nyquist rate which minimizes the amount of information for subsequent transmission, storage, or digital signal processing (DSP).

- 3. Anti-aliasing: The input signals are seldom completely band-limited. Since the modulator is sampling at a rate much higher than the output Nyquist rate, the anti-aliasing filter before the modulator can provide the necessary additional aliasing rejection for the input signal as opposed to the internally generated quantization noise.

The simplest and most economical filter to reduce the input sampling rate is a comb-filter because is not require a multiplier. A multiplier is not required because the filter coefficients are all unity.

The transfer function of a comb-filter is [11]:

$$H(z) = \left(\sum_{i=0}^{N-1} z^{-i}\right)^{M} = \left(\frac{1-z^{-N}}{1-Z^{-1}}\right)^{M}$$

(36)

Where: N is the decimation ratio and M is the order of comb filter.

The algorithm for implementing comb filters is the recursive algorithm. The recursive algorithm with an IIR filter followed by a FIR filter as shown in fig.(3c) [11].

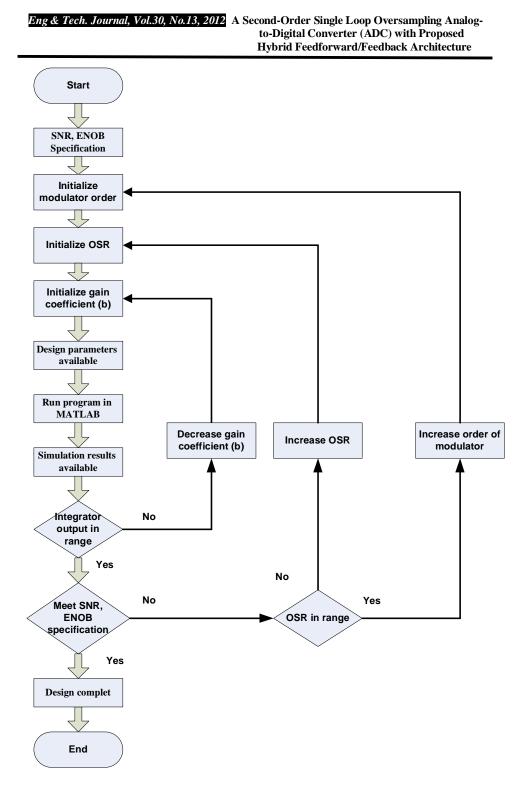

The flow chart of program is shown in fig.(4).

#### SIMULATION RESULTS Without Decimation Filter

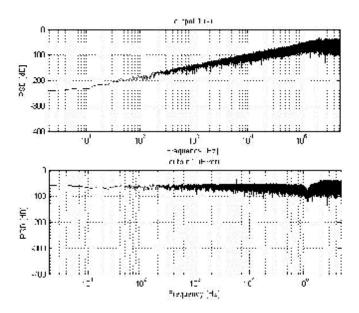

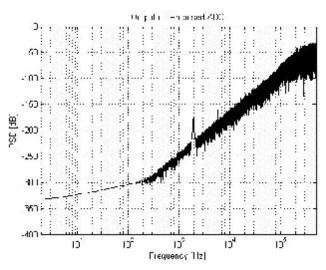

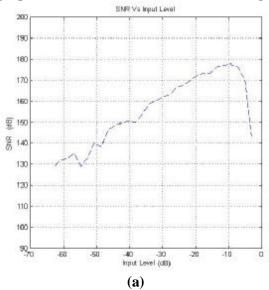

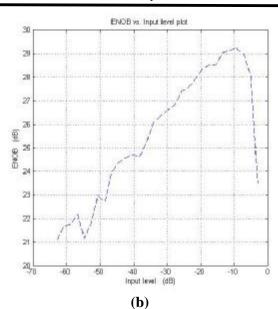

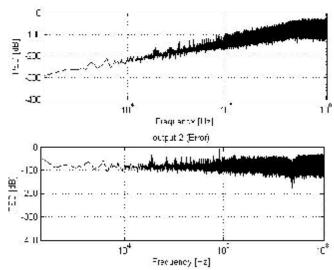

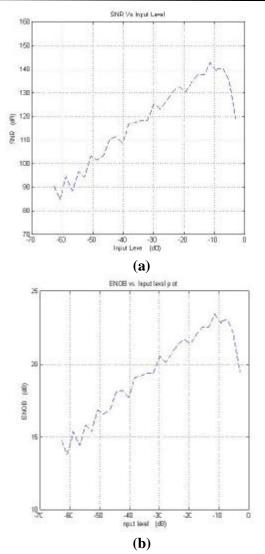

the simulation of proposed This section presents second-order feedforward/feedback ADC without using decimation stage at low OSR, which is suitable for broadband applications [12]. A sinusoidal input with amplitude of 0.7V and a frequency of 1.94 KHz is used. The requirement of the proposed system is summarized in table (1). The measured SNR (by using MATLAB) is 170 db which is equivalent to 28-bit of resolution (by using equation (9)). Fig.(5) shows the quantization noise of the output modulator (y) and the in-band quantization noise error (q). An ECC is proposed for single loop high order modulator to noise shaping the quantization noise of the converter. Fig.(6) shows the in-band noise is perfectly cancelled by using the ECC in output of modulator. Fig.(7) shows the SNR and ENOB versus various input signal power. The final result of simulation of the proposed system is summarized in table (2). With Decimation Filter

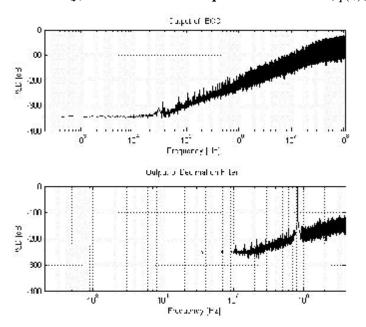

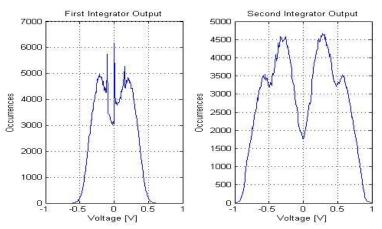

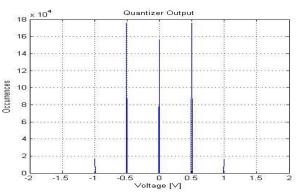

The decimation filter is accomplished by using the MATLAB function (decimate.m). The basic requirement of the proposed system is summarized in table (2). Fig.(8) shows the quantization noise of the output modulator (y) and the in-band quantization noise error (q). An ECC is proposed for single loop high order to noise shaping the quantization noise of the modulator. Fig.(9) shows the in-band noise is perfectly cancelled by using the ECC in output of modulator. Simulation results show an improvement of 139db (by using MATLAB) in SNR at the output of the converter instead of 86 db was design in Ref.[13] and 75 db was design in Ref.[14]. The resolution or ENOB is 22-bit (by using equation (9)). Fig.(10) shows the SNR and ENOB versus various input signal power. The histogram of output of integrators is shown in fig.(11). The output of quantizer is shown in fig.(12). The final result of simulation of the proposed system is summarized in table (4).

### CONCLUSIONS

In this paper a second order analog-to-digital converter type (single-loop high order) with novel feedforward/feedback architecture has been designed and simulated. With high OSR=256, the net improvement in quantization noise reduction is 64 db if compared with feedforward architecture (single-loop second order) was designed in Ref.[6]. The achieved resolution (28-bit) instead of (14-bit) was designed in Ref.[6]. The achieved resolution (28-bit) gives superior performance and suitable to broadband communication applications.

With low OSR=24, the SNR is improved about 55 db if compared with traditional architecture (single-loop third order) was designed in Ref.[13] and 64db if compared with Ref.[14]. The achieved resolution (22-bit)

instead of (14-bit and 12-bit) was designed in Ref.[13] and Ref.[14], respectively.

Finally only one bit quantizer is used in the proposed architecture which greatly decreases the circuit implementation complexity and power consumption.

#### REFERENCES

- [1].Mohammad Yavari and Omid Shoaei, "Low-Voltage Sigma-Delta Modulator Topologies for Broadband Applications', IEEE, ISCAS, 2004.

- [2].Hao-Chiao Hong, Bin-Hong Lin, and Cheng-Wen Wu, "Analysis and Design of Multiple-Bit High-Order -∆ Modulator", IEEE, ASP-DAC, 1997.

- [3].Xiaolong Yuan, "Wideband Sigma-Delta Modulators", Ph.D. Thesis, KTH Information and Communication Technology, 2010.

- [4].Brian Limketkai and Bret Victor, "The Design of A High-Bandwidth Sigma-Delta Modulator", EECS, Project Report 247, December 2000.

- [5].Mucahit Kozak and Izzet Kale, "Oversampled Delta-Sigma Modulators, Analysis, Applications and Novel Topologies", Kluwer academic publishers, 2003.

- [6].Hao Sin, et. al, "Novel Architecture of Feedforward Second-Order Multibit ΔΣAD Modulator", IEICE Trans. Fundamentals, Vol.E91-A, No.4, pp.965-970, April 2008.

- [7]. Chien-Hung Kuo, et. al, "Multi-bit Delta-Sigma Modulator Using a Modified DWA Algorithm", Kluwer Academic Publishers, Analog Integrated Circuits and Signal Processing, pp.289–300, 2002.

- [8].Hon-Weng Chon, et. al, "A1-V 2.56-MHz Clock-Rate CMOS Multi-bit  $\Delta\Sigma$  Modulator With Reset-Opamp Technique And Pseudo Data-Weighted-Averaging For Portable Audio Data Acquisition System", IEEJ, International Analog VLSI Workshop, 2004.

- [9].Mohammad Yavari and Omid Shoaei, "The Design of Sigma-Delta Analog to Digital Converters for Digital Audio", IEEE, ISCAS, 2004.

- [10]. Sangil Park, "Principles of Sigma-Delta Modulation for Analog-to-Digital Converters", Motorola, Inc., Application Note APR8, 1997.

- [11]. Yonghong Gao and Hannu Tenhunen, "Low-Power Implementation of a Fifth-Order Comb Decimation Filter for Multi-Standard Transceiver Applications", Electronic System Design Laboratory, Royal Institute of Technology, 1999.

- [12]. Anas A. Hamoui and Kenneth W. Martin, "High-Order Multibit Modulators and Pseudo Data-Weighted-Averaging in Low-Oversampling  $\Delta\Sigma$  ADCs for Broad-Band Applications", IEEE, Vol. 51, No. 1, January 2004.

#### Eng & Tech. Journal, Vol.30, No.13, 2012 A Second-Order Single Loop Oversampling Analogto-Digital Converter (ADC) with Proposed Hybrid Feedforward/Feedback Architecture

- [13]. Soon Jai Yi, et. al, "A 3rd order 3bit Sigma-Delta Modulator with Reduced Delay Time of Data Weighted Averaging", World Academy of Science, Engineering and Technology, No.71, 2010.

- [14]. Sejin Jo, et. al, "A 3rd 3bit Sigma-Delta Modulator with Data Weighted Averaging for Reducing Delay Time", CISST, 2010.

Eng & Tech. Journal, Vol.30, No.13, 2012 A Second-Order Single Loop Oversampling Analogto-Digital Converter (ADC) with Proposed Hybrid Feedforward/Feedback Architecture

(c)

Figure (2): (a) Conventional feedback second order single loop [6], (b) feedforward second order single loop [6] (c) Proposed hybrid (I) feedforword/feedback second order single loop modulator.

**(a)**

(c)

Figure(3): Proposed architecture (a) Proposed hybrid (I) feedforword/feedback ADC type (second order single-loop) with ECC, (b) Proposed (II) error cancellation circuit (ECC) with decimation filter, (c) Block diagram of one-stage comb-filter [11,12].

Figure (4): Flow chart of the simulation program.

Unit

Parameters

This work

Ref.[6]

Order

Second

Second

Type

Feedforward/Feedback Single-loop

Feedforward Single-loop

OSR

256

256

1.94KHz

1.24MHz

Not defined

2KHz

Table (1): The basic requirements of proposed oversampling ADC.

1.94KHz

1.24MHz

2KHz

-7dB

Figure (5): Simulation of quantization noise spectrum of the modulator (y) And in-band error quantization noise (q(z)).

ADC

Input

frequency

Bandwidth

Sampling frequency

Input signal level

signal

Eng & Tech. Journal, Vol.30, No.13, 2012 A Second-Order Single Loop Oversampling Analogto-Digital Converter (ADC) with Proposed Hybrid Feedforward/Feedback Architecture

Figure (6): Simulation of quantization noise spectrum of the proposed novel ADC without decimation stage.

Figure(7): (a) The SNR versus the input signal power, (b) The ENOB versus the input signal power.

| Tuble (2): Summarizes the simulation results: |               |               |  |  |

|-----------------------------------------------|---------------|---------------|--|--|

| Parameter                                     | This work     | Ref.[6]       |  |  |

| ENOB                                          | 28-bit        | 14-bit        |  |  |

| SNR                                           | 170dB         | 106dB         |  |  |

| Noise                                         | -250dB@100KHz | -120dB@100KHz |  |  |

| Order                                         | Second        | Second        |  |  |

| Quantizer                                     | 1-bit         | 3-bit         |  |  |

Table (2): Summarizes the simulation results.

Table (3): The basic requirements of proposed oversampling ADC.

| Unit | Parameters             | This work without DWA                 | Ref.[13] without DWA | Ref.[14] with DWA    |

|------|------------------------|---------------------------------------|----------------------|----------------------|

| ADC  | order                  | Second                                | Third                | Third                |

|      | type                   | Feedforward/Feedback -Single-<br>loop | Feedback Single-loop | Feedback Single-loop |

|      | OSR                    | 24                                    | 24                   | 24                   |

|      | Input signal frequency | 825KHz                                | 825KHz               | 825KHz               |

|      | Sampling frequency     | 52.8 MHz                              | 52.8 MHz             | 52.8 MHz             |

|      | Bandwidth              | 1.1MHz                                | 1.1MHz               | 1.1MHz               |

|      | Input signal level     | -7dB                                  | -6dB                 | -6dB                 |

|      |                        | Decimation ratio (N)=4                |                      |                      |

|      | Decimation filter      | Order of filter $(M) = 30$            | Not used             | Not used             |

|      |                        | Cut-off frequency $(W_n)=0.25$        |                      |                      |

Figure(8): Simulation of quantization noise spectrum of the modulator (y) and in-band error quantization noise (q(z)).

Figure (9): Simulation of quantization noise spectrum of the ECC and decimation filter.

Eng & Tech. Journal, Vol.30, No.13, 2012 A Second-Order Single Loop Oversampling Analogto-Digital Converter (ADC) with Proposed Hybrid Feedforward/Feedback Architecture

Figure (10): (a) The SNR versus the input signal power, (b) The ENOB versus the input signal power.

Figure (11): The output level histograms of the first and second integrators for proposed ADC.

Figure (12): The output level histogram of quantizer.

| Parameter | This work    | Ref.[13]      | Ref.[14]     |

|-----------|--------------|---------------|--------------|

| ENOB      | 22-bit       | 14-bit        | 12-bit       |

| SNR       | 139dB        | 84dB          | 75 dB        |

| Noise     | -            | -120dB@100KHz | -            |

|           | 250dB@100KHz |               | 100dB@100KHz |

| Order     | Second       | Third         | Third        |

| Quantizer | 1-bit        | 3-bit         | 3-bit        |

Table (4): Summarizes the simulation results.